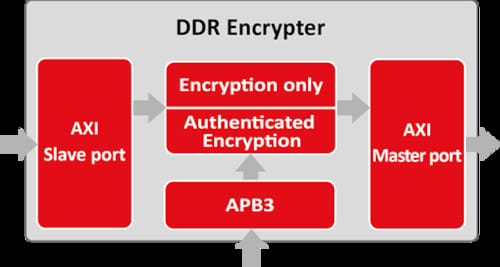

Con un ancho de bus de datos escalable, el encriptador DDR para sistemas ASIC/FPGA dispone de un núcleo IP altamente escalable.

Silex Insight, proveedor de soluciones IP para seguridad en sistemas embebidos, anuncia el lanzamiento de su nuevo encriptador DDR pensado para su uso en sistemas de alto rendimiento (ASIC/FPGA).

Presenta un gran ancho de banda, de hasta 100 Gbps, y facilita la capacidad de su módulo de encriptación DDR para IP Core para realizar la encriptación y autenticación sobre la marcha a una memoria externa.

Además, es altamente configurable y puede ser optimizado para varios intercambios de tamaño, rendimiento, y latencia. El núcleo es independiente de dispositivo y altamente portable.

Entre las funcionalidades que ofrece este encriptador DDR para sistemas ASIC/FPGA tenemos la protección de la memoria externa, el ancho escalable del bus de datos (de 32, 64, o 128 bits), cuenta con interfaces AMBA maestro/esclavo, administración de múltiples regiones, y es transparente al procesador.

Por otro lado, las áreas de aplicación para las que lo podemos emplear tenemos los centros de datos, los sistemas de pago, o el sector de la defensa.

Otras posibilidades de uso y aplicación

Muchos dispositivos ASIC/FPGA son ahora SoCs (System-on-Chip) que contienen un bloque de procesamiento integrado. Cuando la confidencialidad de los datos es esencial, esta se protege de los accesos a la memoria realizados por el procesador. Dichos accesos pueden provocarse por búsquedas de instrucciones de procesador o transacciones generales de la memoria.

Este núcleo IP mejora la resistencia a la manipulación al evitar cualquier modificación, falsificación o análisis de datos externos. Viene con capacidad opcional de autenticación y es capaz de gestionar administración multi-región. El núcleo IP es altamente configurable con la posibilidad de intercambios de área/rendimiento.

Además de soportar las interfaces AXI master/slave, también cuenta con un puerto APB para las tareas de configuración. Su ubicación típica es entre él o los procesadores, y un controlador de memoria externa (DDRx).

Finalmente, tenemos toda la información sobre este encriptador DDR de memoria en su página web.